Import HDL Files or IP Cores

Video Guides

VHDL with the VHDPlus IDE

Verilog with the VHDPlus IDE

Import a HDL file (VHDL, Verilog)

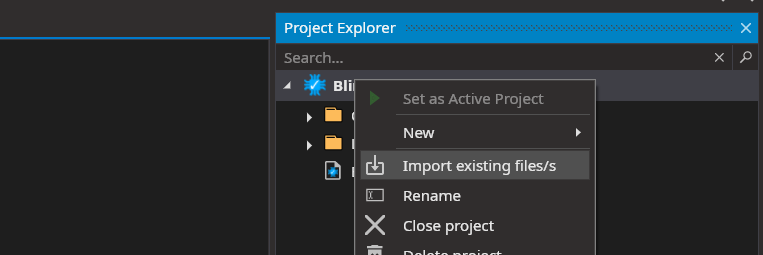

- Right-click the project or a folder in the project explorer

- Click on "Import existing file/s"

- Set HDL Files as filter and select the HDL file to import

- Now when you write

NewComponentin your VHDP code, the VHDL component should show up

Import other HDL files

- Right-click the project or a folder in the project explorer

- Click on "Import existing file/s"

- Set All Files as filter and select the HDL file to import

- To add the file like a VHDP

Component, you have to write a VHDP interface:- Create a new VHDP file

- Rename it so the file extension is .qsys.vhdp

- Add a

Componentin the file with the name of the component in the HDL file and add the signals and generic parameters from the HDL file

- Now when you write

NewComponentin your VHDP code, the new component should show up

Example for DVI_OUT.v:

Component DVI_OUT

(

iPCLK : IN STD_LOGIC;

iSCLK : IN STD_LOGIC;

iRED : IN STD_LOGIC_VECTOR(7 downto 0);

iGRN : IN STD_LOGIC_VECTOR(7 downto 0);

iBLU : IN STD_LOGIC_VECTOR(7 downto 0);

iHS : IN STD_LOGIC;

iVS : IN STD_LOGIC;

iDE : IN STD_LOGIC;

oDVI_DATA : OUT STD_LOGIC_VECTOR(2 downto 0);

oDVI_CLK : OUT STD_LOGIC;

iDVI_HPD : IN STD_LOGIC;

)

{

}

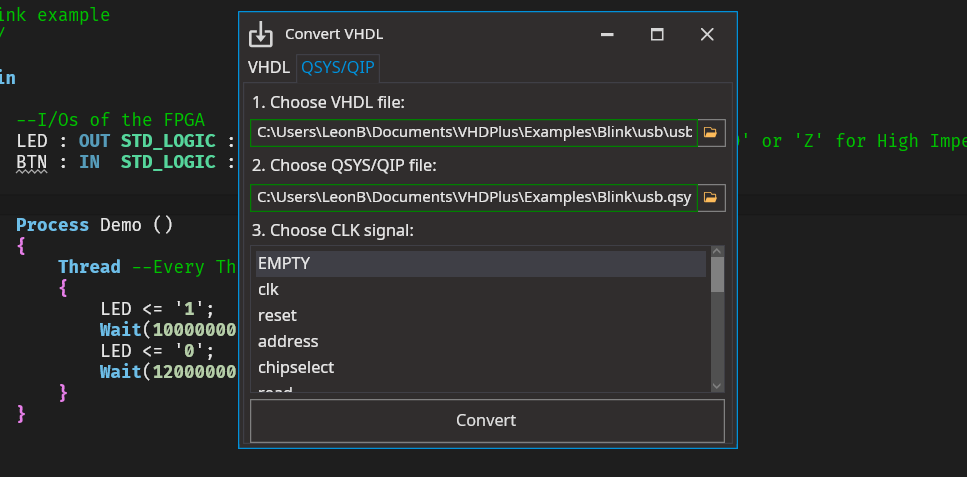

You can use this tool to import existing VHDL files or Intel FPGA IP Cores and convert them to be used in your project.

Convert a VHDL file to use it like a VHDP file

- Select the VHDL file

- Choose a signal that should be connected with the CLK signal (or EMPTY to keep all inputs)

- Press

Convert. The converted file will be added to the active project.

Import an Intel FPGA IP Cores

- Open Quartus with the current project (Tools/Open in Quartus)

- Select an IP Core from the IP Catalog (Tools/IP Catalog)

- Generate the QSYS/QIP file and the VHDL file by following the assistant

- Go to the import tool and select the generated VHDL file and the QSYS/QIP file

- Choose a signal that should be connected with the CLK signal (or EMPTY to keep all inputs)

- Press

Convert. The QSYS/QIP file will be added to the project as link to the IP Core and a VHDP file will be generated as interface so you can use the IP Core in the VHDP files. If you want to change the parameters you can open the QSYS/QIP file from the project explorer. Make sure that the I/Os of the VHDP file are still correct.